SK Hynix: We're Planning for DDR5-8400 at 1.1 Volts

by Gavin Bonshor on April 3, 2020 1:15 PM EST

Back in November last year, we reported that SK Hynix had developed and deployed its first DDR5 DRAM. Fast forward to the present, and we also know SK Hynix has recently been working on its DDR5-6400 DRAM, but today the company has showcased that it has plans to offer up to DDR5-8400, with on-die ECC, and an operating voltage of just 1.1 Volts.

WIth CPU core counts rising with the fierce battle ongoing between Intel and AMD in the desktop, professional, and now mobile markets, the demand to increase throughput performance is high on the agenda. Memory bandwidth by comparison has not been increasing as much, and at some level the beast needs to be fed. Announcing more technical details on its official website, SK Hynix has been working diligently on perfecting its DDR5 chips with capacity for up to 64 Gb per chip.

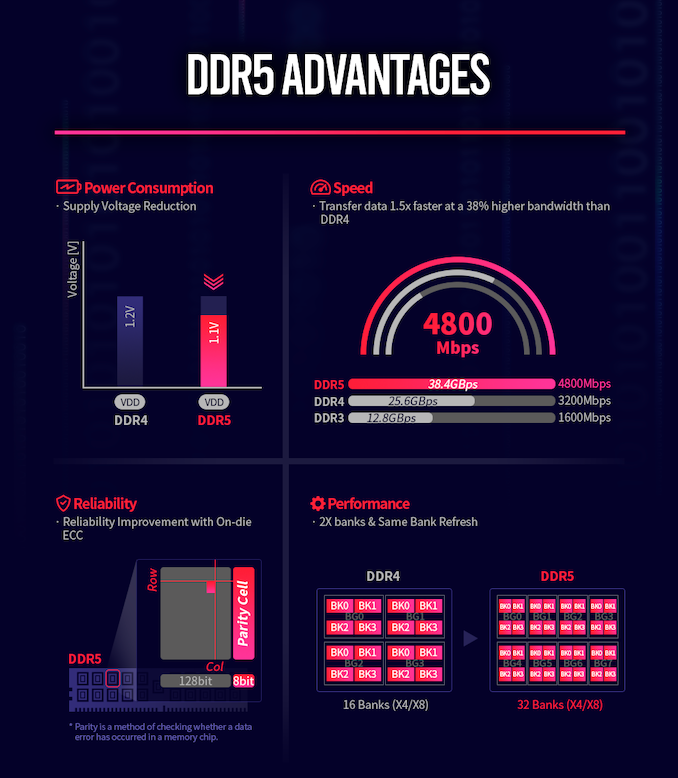

SK Hynix had previously been working on its DDR5-6400 DRAM, which has 16 Gb which is formed of 32 banks, with 8 bank groups, with double the available bandwidth and access potential when compared with DDR4-3200 memory. For reference, DDR4 uses 16 banks with 4 bank groups. The key solution to improve access throughout is the burst length, which has been doubled to 16 when compared with 8 on DDR4. Another element to consider is DDR4 can't by proxy run operations while it's refreshing. DDR5 is using SBRF (same bank refresh function) which allows the system the ability to use other banks while one is refreshing, which in theory improves memory access availability.

As we've already mentioned, SK Hynix already has DDR5-6400 in its sights which are built upon its second-generation 10nm class fabrication node. SK Hynix has now listed that it plans to develop up to DDR5-8400. Similar in methodology to its DDR5-6400 DRAM, DDR5-8400 requires much more forethought and application. What's interesting about SK Hynix's DDR5-8400 is the jump in memory banks, with DDR5-8400 using 32 banks, with 8 bank groups.

Not just content at increasing overall memory bandwidth and access performance over DDR4, the new DDR5 will run with an operating voltage of 1.1 V. This marks a 9% reduction versus DDR4's operating voltage which is designed to make DDR5 more power-efficient, with SK Hynix reporting that it aims to reduce power consumption per bandwidth by over 20% over DDR4.

To improve performance and increase reliability in server scenarios, DDR5-8400 will use on-die ECC (Error Correction) and ECS (Error Check and Scrub) which is a milestone in the production of DDR5. This is expected to reduce overall costs, with ECS recording any defects present and sends the error count to the host. This is designed to improve transparency with the aim of providing enhanced reliability and serviceability within a server system. Also integrated into the design of the DDR5-8400 DRAM is Decision Feedback Equalization (DFE), which is designed to eliminate reflective noise when running at high speeds. SK Hynix notes that this increases the speed per pin by a large amount.

In the above image from specification comparison between DDR4 and DDR5 from SK Hynix, one interesting thing to note is that it mentions DRAM chips with density up to 64 gigabit. We already know that the chip size of DDR5 is 65.22mm², with a data rate of 6.4 Gbps per pin, and uses its 1y-nm 4-metal DRAM manufacturing process. It is worth pointing out that the DDR5-5200 RDIMM we reported on back in November 18, uses 16 Gb DRAM chips, with further scope to 32 Gb reported. SK Hynix aims to double this to 64 Gb chips which do double the density, at lower power with 1.1 volts.

Head of DRAM Product Planning at SK Hynix, Sungsoo Ryu stated that:

"In the 4th Industrial Revolution, which is represented by 5G, autonomous vehicle, AI, augmented reality (AR), virtual reality (VR), big data, and other applications, DDR5 DRAM can be utilized for next-gen high-performance computing and AI-based data analysis".

SK Hynix if still on schedule with the current Coronavirus COVID-19 pandemic, looks set to enter mass production of DDR5 later this year.

Related Reading

Source: SK Hynix

84 Comments

View All Comments

InTheMidstOfTheInBeforeCrowd - Saturday, April 4, 2020 - link

Also, what's that?> Thus, a many core chip could have a very low resistance and use even more power than a low core count chip with a higher voltage.

You know what too has a very low resistance (relatively speaking)? Mains wiring. So, does mains wiring use a lot of power? No. Why not? It has such a low resistance... Why is the mains wiring not using more power than, for example, a vacuum cleaner, despite the mains wiring clearly and measurable having a much lower resistance than the vacuum cleaner? Me thinks, you need some more coffee ;-)

willis936 - Saturday, April 4, 2020 - link

Because the voltage drop on mains is low. P = V^2/R. A vacuum cleaner has a high voltage drop and low resistance.Anyway, your original point is correct. Dynamic power is dominant in current CPUs. See: the wikipedia page I linked (and ones it links).

Drazen - Saturday, April 4, 2020 - link

Let me simplify. DC power is measured in W (Watt) while AC power in VA (volt amper). Digital electronics is combination of both. Today most of digital is produced in CMOS where most of current is consumed while switching from 0 -> 1 and 1 -> 0.In steady state almost no current flows. Power consumption is almost linear to frequency. But in circuits situation is different cause of trace inductance and capacitance, decoupling capacitors, etc.When CMOS changes state for brief period of time both transistors are conductive and current spike occurs. Trace inductance (traces in chip, bonding wires, pads, PCB traces) tries to reduce current (purpose of inductor) and this lowers voltage. Decoupling caps are used to supply power for this brief period and a bit later when both transistor are closed cap starts to charge from power supply. Result is a lot of oscillations - spurs.

Caps (any two separated conductors) on other side destroy change in voltage - smooth voltage change.

Inside chip that's not so big problem as is between chips. That's reason why memories are as close as to the CPU. And here comes problem when distance is larger, eg PCIE, SATA. Only way to transmit signal is to switch to sinusoidal currents, lower voltage and use two wires to reduce generated noise (single wire behaves as an antenna). This is called differential signaling. Longer wires require more power to fight cable inductance/capacitance. And amplifiers at both ends.

x570 motherboards already have huge problems cause of PCIE4 which is already designed with this purpose but DDR is not.

Above I wrote that digital is using digital signal, 0 and 1, but at high speed and a bit longer wire signal becomes analog, sinusoidal. This requires PCIE like signals or very expensive motherboards and for sure some error detection and correction. 8.4GHz single ended is really big task for PCB design.

Let's see but it won't be cheap. Today DDR at 3600 has problems and only few motherboards work reliably.

supdawgwtfd - Saturday, April 4, 2020 - link

Watts can be used for both DC and AC...It is a measure of power.

Not just electrical power either.

Not sure where you got the idea that AC is volt amps...

Never need anything (other than UPS's outputs) reference volt amps.

jhensjh - Sunday, April 5, 2020 - link

Watts are the unit of measure of power in both AC and DC. The volt ampere is a different unit and is used to measure apparent power. Apparent power has two components, one of which is the real power measured in watts. The other component of apparent power is reactive power, measured in volt-ampere reactive (VAR).Zoolook - Wednesday, May 6, 2020 - link

You are confusing Data rate with frequency, the signaling of DDR3200 is 1,6 GHz the Data rate is 3,2GHz. You are correct that signaling of 8.4GHz would be very difficult, luckily we don't need that fast signaling for DDR5.back2future - Friday, June 12, 2020 - link

Who is getting best solutions therefore? Fuzzy layers towards memory connectors (or at least partly integrated into cpu being L4 cache), for interconnecting cores on different sockets and towards peripherals on pcbs? Interesting times on that level, thxlinuxgeex - Tuesday, April 7, 2020 - link

A vacuum cleaner has a High Resistance (at startup, thanks to either a motor start capacitor or a varistor) which prevents it from drawing so much power that it would blow the fuse or melt the windings. Once the motor has spun up a bit the Resistance drops, and instead Back EMF from the rotor's magnetic fields rotating relative to the windings, creates high Impedance, which effectively resists current flow and prevents the motor spinning faster than its rated maximum unloaded RPMs.At that max rate of rotation, the motor draws the least power thanks to that high impedance. It also has the least torque, which is why the frequency of the vacuum motor climbs so much when you block the nozzle - very little work can be done in that high RPM range. Kinda the opposite of a car engine. Anyhow, voltage drop is very low when the vacuum cleaner has finished spinning up, and it's even lower than that when you block the nozzle. For a big voltage drop - try a K15 kettle.

back2future - Friday, June 12, 2020 - link

Consumption (and average power) will differ for task dependent customer profiles, e.g. server or office desktop or mobile usage patterns, having lower and upper limits (for to ask experts therefore). Considering upper limits coming close to steady full power what ringing/settling time and time to (first) reach this state on usage patterns, (secondly) what are safety margins and (thirdly) what effects on aging stability compared to DDR4 are to be expected?(Don't know, if these questions are worked on, outside probably NDA manuals, if at all?)

S20802 - Friday, April 3, 2020 - link

Lol "source" SK Hynix Link goes back to Anandtech