DFI X48 LT T2R: Floats like a Butterfly…

by Rajinder Gill on April 28, 2008 4:00 AM EST- Posted in

- Motherboards

Performance Level

Leaving this function set to Auto works okay as long as the board is not going to be pushed. One of the issues pertaining to the current BIOS is that the BIOS automatically applies tRD Phase shifts (see the AUTO section below), which prevent the user from running a flat Performance Level unless a value is selected 1 higher than the required value and all the Phase Shift Registers (at least the active ones according to the memory divider) are set to Enabled. So, if you want to run a Performance Level of 7, select 8 and then proceed to set all the tRD Phase shift registers to Enabled, which will in fact give you a tRD of 7.

If the registers are left at AUTO, there's a good chance that the board will fail to POST at higher FSB speeds that happen to fall at the limit of the applied level of tRD. For example if the limit of tRD 6 happens to be at 450 FSB and tRD phase shifts are left to AUTO, some of the channels will pull down to a tRD of 5 resulting in either a non-POST or a system hang during OS loading.

|

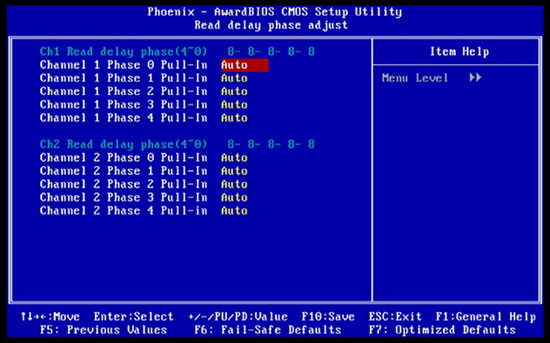

TRD Phase Adjust

This BIOS function is best explored by more advanced tweakers and benchmarkers; our own findings are as follows.

Options for this function are AUTO and ENABLED

Default for all phases is AUTO

AUTO: Unlike the DFI P35 T2R BIOS, setting AUTO will not disable the function of the tRD Phase shift registers; rather the BIOS attempts to apply any phase shifts it thinks are possible. While this works well for the most part, there are times when overclocking that increasing the Performance Level by 1 in the DRAM timing page and setting all the phases to Enabled may be the best course of action.

ENABLED: Sets the corresponding phase of the TRD cycle to -1. If we set a Performance Level of 7 in the DRAM page, using ENABLED for any of the phases will set the Performance Level of the selected Phase to 6, i.e. TRD -1 for the corresponding phase and channel.

Both channels have independent phase adjustments, and the maximum advantage of setting a phase to ENABLED occurs when the same phase from both channels is set to ENABLED simultaneously. Please note not all of the phases are active at all times. The number of active phases is dependent on the memory divider used i.e. the number of FSB cycles that are active in relation to the number of active memory bus cycles.

24 Comments

View All Comments

lopri - Monday, April 28, 2008 - link

Sorry if I missed it but I can't locate it?Rajinder Gill - Monday, April 28, 2008 - link

Hi,There is no PDF, it is an Adobe flash player video on page 14..

regards

Raja

Kromis - Monday, April 28, 2008 - link

I'm loving the green!Kromis - Monday, April 28, 2008 - link

I haven't heard/read much from DFI in a while